# (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 110164900 A (43)申请公布日 2019.08.23

(21)申请号 201910456585.0

(22)申请日 2019.05.29

(71)申请人 京东方科技集团股份有限公司 地址 100015 北京市朝阳区酒仙桥路10号

(72)发明人 侯孟军 李延钊 孟虎 刘宗民

(74)专利代理机构 北京中博世达专利商标代理 有限公司 11274

代理人 申健

(51) Int.CI.

H01L 27/15(2006.01)

H01L 33/00(2010.01)

H01L 33/20(2010.01)

权利要求书2页 说明书11页 附图6页

#### (54)发明名称

LED芯片及其制备方法、芯片晶圆、Micro-LED显示装置

#### (57)摘要

本发明实施例提供一种LED芯片及其制备方 法、芯片晶圆、Micro-LED显示装置,涉及显示技 术领域,可以解决LED芯片侧壁受损形成漏电通 道,进而影响LED芯片的发光效率的问题。该LED 芯片包括依次层叠设置的第一电极、第一半导体 图案、发光图案、第二半导体图案以及第二电极; 第一电极与第一半导体图案接触,第二电极与第 二半导体图案接触,第二电极为透明电极;第一 半导体图案和/或第二半导体图案在发光图案上 的正投影的边界位于发光图案的边界以内;第一 半导体图案、第二半导体图案以及发光图案沿 V LED芯片的厚度方向具有重叠区域;第一半导体 图案为n型半导体,第二半导体图案为p型半导 体:或者,第一半导体图案为p型半导体,第二半 导体图案为n型半导体。

1.一种LED芯片,其特征在于,包括依次层叠设置的第一电极、第一半导体图案、发光图案、第二半导体图案以及第二电极;所述第一电极与所述第一半导体图案接触,所述第二电极与所述第二半导体图案接触,所述第二电极为透明电极;

所述第一半导体图案和/或所述第二半导体图案在所述发光图案上的正投影的边界位于所述发光图案的边界以内;所述第一半导体图案、所述第二半导体图案以及所述发光图案沿所述LED芯片的厚度方向具有重叠区域;

其中,所述第一半导体图案为n型半导体,所述第二半导体图案为p型半导体;或者,所述第一半导体图案为p型半导体,所述第二半导体图案为n型半导体。

2.根据权利要求1所述的LED芯片,其特征在于,所述第二半导体图案在所述发光图案 上的正投影的边界位于所述发光图案的边界以内;

所述第一半导体图案在所述发光图案上的正投影的边界与所述发光图案的边界重叠。

- 3.根据权利要求2所述的LED芯片,其特征在于,所述第二半导体图案在所述发光图案上的正投影的边界与靠近该边界的所述发光图案的边界沿第一方向的距离为所述第二半导体图案沿所述第一方向的长度的0.5倍~3倍。

- 4.根据权利要求2所述的LED芯片,其特征在于,所述LED芯片还包括设置在所述第二半导体图案上的黑矩阵图案;

所述第二半导体图案在所述黑矩阵图案上的正投影位于所述黑矩阵图案的镂空区域内。

- 5.根据权利要求1-4任一项所述的LED芯片,其特征在于,所述第一电极为反射电极。

- 6.一种芯片晶圆,其特征在于,包括衬底以及设置在所述衬底上的多个如权利要求1-5 任一项所述的LED芯片:

第一半导体图案与所述衬底接触,第一电极穿过所述衬底上的过孔与所述第一半导体图案接触。

- 7.一种Micro-LED显示装置,其特征在于,包括电路基板以及设置在所述电路基板上的 多个如权利要求1-5任一项所述的LED芯片。

- 8.一种LED芯片的制备方法,其特征在于,包括:

在衬底上形成多个层叠设置的第一半导体图案、发光图案和第二半导体图案;所述第一半导体图案和/或所述第二半导体图案在所述发光图案上的正投影的边界位于所述发光图案的边界以内;所述第一半导体图案为n型半导体,所述第二半导体图案为p型半导体;或者,所述第一半导体图案为p型半导体,所述第二半导体图案为n型半导体;

在每个所述第二半导体图案上形成第二电极;所述第二电极与所述第二半导体图案接触;所述第二电极为透明电极;

在每个所述第一半导体图案远离所述发光图案的一侧形成第一电极,所述第一电极与 所述第一半导体图案接触,并去除所述衬底,以形成多个LED芯片。

9.根据权利要求8所述的LED芯片的制备方法,其特征在于,所述在每个所述第一半导体图案远离所述发光图案的一侧形成第一电极,所述第一电极与所述第一半导体图案接触,并去除所述衬底,以形成多个LED芯片,包括:

在所述衬底上形成多个过孔,以露出每个所述第一半导体图案;

在每个所述过孔处形成所述第一电极,所述第一电极穿过所述衬底上的过孔与所述第

## 一半导体图案接触;

去除所述衬底,以形成多个所述LED芯片。

10.根据权利要求8所述的LED芯片的制备方法,其特征在于,所述在衬底上形成多个层叠设置的第一半导体图案、发光图案和第二半导体图案,包括:

在所述衬底上依次形成第一半导体层、发光层以及第二半导体层;

对所述第二半导体层进行构图形成多个所述第二半导体图案;

对所述第一半导体层和所述发光层同时进行构图形成多个所述发光图案和多个所述 第一半导体图案;所述第二半导体图案在所述衬底上的正投影的边界位于所述发光图案在 所述衬底上的正投影的边界以内。

11.根据权利要求10所述的LED芯片的制备方法,其特征在于,在形成所述第二半导体图案之后,去除所述衬底之前,所述LED芯片的制备方法还包括:

在所述第二半导体图案上形成黑矩阵图案;所述第二半导体图案在所述衬底上的正投影位于所述黑矩阵图案的镂空区域在所述衬底上的正投影内。

# LED芯片及其制备方法、芯片晶圆、Micro-LED显示装置

## 技术领域

[0001] 本发明涉及显示技术领域,尤其涉及一种LED芯片及其制备方法、芯片晶圆、Micro-LED显示装置。

## 背景技术

[0002] 发光二极管 (Light Emitting Diode, 简称LED) 是一种能够将电能转换成特定波长范围的光的半导体元件。发光二极管的发光原理是电子和空穴复合发光。

[0003] 发光二极管具有低功耗、尺寸小、亮度高、易与集成电路匹配及可靠性高等优点,目前常作为光源被广泛应用。随着LED技术的成熟,直接使用LED作为亚像素的LED显示装置或Micro-LED(微型LED)显示装置逐渐发展起来。

#### 发明内容

[0004] 本发明的实施例提供一种LED芯片及其制备方法、芯片晶圆、Micro-LED显示装置,可以解决LED芯片侧壁受损形成漏电通道,进而影响LED芯片的发光效率的问题。

[0005] 为达到上述目的,本发明的实施例采用如下技术方案:

[0006] 第一方面,提供一种LED芯片,包括依次层叠设置的第一电极、第一半导体图案、发光图案、第二半导体图案以及第二电极;所述第一电极与所述第一半导体图案接触,所述第二电极与所述第一半导体图案接触,所述第二电极为透明电极;所述第一半导体图案和/或所述第二半导体图案在所述发光图案上的正投影的边界位于所述发光图案的边界以内;所述第一半导体图案、所述第二半导体图案以及所述发光图案沿所述LED芯片的厚度方向具有重叠区域;其中,所述第一半导体图案为n型半导体,所述第二半导体图案为p型半导体;或者,所述第一半导体图案为p型半导体,所述第二半导体图案为n型半导体。

[0007] 在一些实施例中,所述第二半导体图案在所述发光图案上的正投影的边界位于所述发光图案的边界以内;所述第一半导体图案在所述发光图案上的正投影的边界与所述发光图案的边界重叠。

[0008] 在一些实施例中,所述第二半导体图案在所述发光图案上的正投影的边界与靠近该边界的所述发光图案的边界沿第一方向的距离为所述第二半导体图案沿所述第一方向的长度的0.5倍~3倍。

[0009] 在一些实施例中,所述LED芯片还包括设置在所述第二半导体图案上的黑矩阵图案,所述第二半导体图案在所述黑矩阵图案上的正投影位于所述黑矩阵图案的镂空区域内。

[0010] 在一些实施例中,所述第一电极为反射电极。

[0011] 第二方面,提供一种芯片晶圆,包括衬底以及设置在所述衬底上的多个上述的LED 芯片;第一半导体图案与所述衬底接触,第一电极穿过所述衬底上的过孔与所述第一半导体图案接触。

[0012] 第三方面,提供一种Micro-LED显示装置,包括电路基板以及设置在所述电路基板

上的多个上述的LED芯片。

[0013] 第四方面,提供一种LED芯片的制备方法,包括:在衬底上形成多个层叠设置的第一半导体图案、发光图案和第二半导体图案;所述第一半导体图案和/或所述第二半导体图案在所述发光图案上的正投影的边界位于所述发光图案的边界以内;所述第一半导体图案为n型半导体,所述第二半导体图案为p型半导体;或者,所述第一半导体图案为p型半导体,所述第二半导体图案为n型半导体;在每个所述第二半导体图案上形成第二电极;所述第二电极与所述第二半导体图案接触;所述第二电极为透明电极;在每个所述第一半导体图案接触,并去陷所述发光图案的一侧形成第一电极,所述第一电极与所述第一半导体图案接触,并去除所述衬底,以形成多个LED芯片。

[0014] 在一些实施例中,所述在每个所述第一半导体图案远离所述发光图案的一侧形成第一电极,所述第一电极与所述第一半导体图案接触,并去除所述衬底,以形成多个LED芯片,包括:在所述衬底上形成多个过孔,以露出每个所述第一半导体图案;在每个所述过孔处形成所述第一电极,所述第一电极穿过所述衬底上的过孔与所述第一半导体图案接触;去除所述衬底,以形成多个所述LED芯片。

[0015] 在一些实施例中,所述在衬底上形成多个层叠设置的第一半导体图案、发光图案和第二半导体图案,包括:在所述衬底上依次形成第一半导体层、发光层以及第二半导体层;对所述第二半导体层进行构图形成多个所述第二半导体图案;对所述第一半导体层和所述发光层同时进行构图形成多个所述发光图案和多个所述第一半导体图案;所述第二半导体图案在所述衬底上的正投影的边界位于所述发光图案在所述衬底上的正投影的边界以内。

[0016] 在一些实施例中,在形成所述第二半导体图案之后,去除所述衬底之前,所述LED 芯片的制备方法还包括:在所述第二半导体图案上形成黑矩阵图案;所述第二半导体图案 在所述衬底上的正投影位于所述黑矩阵图案的镂空区域在所述衬底上的正投影内。

[0017] 本发明实施例提供一种LED芯片及其制备方法、芯片晶圆、Micro-LED显示装置,LED芯片包括依次层叠设置的第一电极、第一半导体图案、发光图案、第二半导体图案以及第二电极,第一半导体图案和/或第二半导体图案在发光图案上的正投影的边界位于发光图案的边界以内。由于第一半导体图案和/或第二半导体图案在发光图案上的正投影的边界位于发光图案的边界以内,且第一半导体图案、第二半导体图案以及发光图案沿LED芯片的厚度方向具有重叠区域,因而第一半导体图案、第二半导体图案以及发光图案沿LED芯片的厚度方向未完全重叠的区域(即非像素区域)包围第一半导体图案、第二半导体图案以及发光图案沿LED芯片的厚度方向未完全重叠的区域(即像素区域),而载流子主要在第一半导体图案、第二半导体图案以及发光图案沿LED芯片的厚度方向重叠的区域发生复合并发光(即在像素区域发生复合并发光),在第一半导体图案、第二半导体图案以及发光图案沿LED芯片的厚度方向未完全重叠的区域不发生复合或复合的较少(即在非像素区域不发生复合或复合的较少),因而LED芯片中的第一半导体图案、发光图案和第二半导体图案的侧壁结构受到损伤后,对第一半导体图案、第二半导体图案以及发光图案沿LED芯片的厚度方向重叠的区域的载流子的复合影响较小,因而相对于相关技术提高了LED芯片的发光效率。

## 附图说明

[0018] 为了更清楚地说明本发明实施例或相关技术中的技术方案,下面将对实施例或相关技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

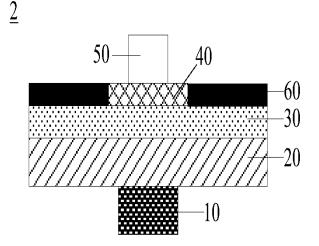

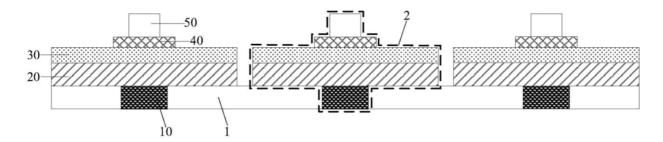

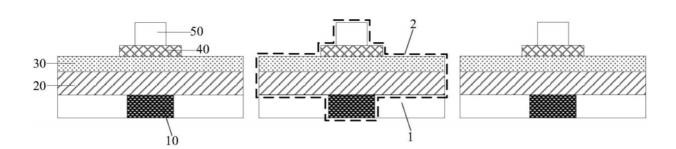

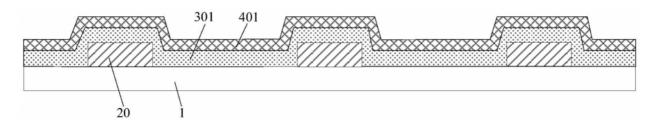

[0019] 图1为本发明实施例提供的一种芯片晶圆的结构示意图;

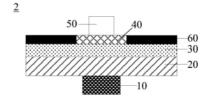

[0020] 图2为本发明实施例提供的一种对芯片晶圆进行处理形成多个LED芯片的结构示 意图:

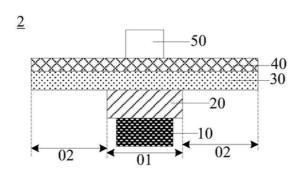

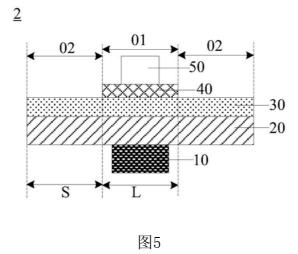

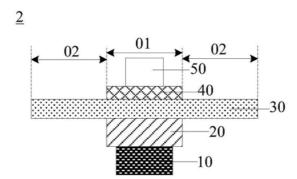

[0021] 图3为本发明实施例提供的另一种对芯片晶圆进行处理形成多个LED芯片的结构示意图;

[0022] 图4为本发明实施例提供的一种LED芯片的结构示意图一:

[0023] 图5为本发明实施例提供的一种LED芯片的结构示意图二;

[0024] 图6为本发明实施例提供的一种LED芯片的结构示意图三;

[0025] 图7为相关技术提供的一种LED芯片的结构示意图;

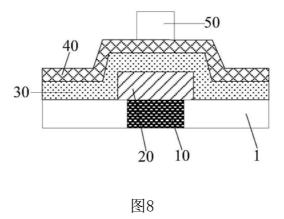

[0026] 图8为本发明实施例提供的一种LED芯片的结构示意图四;

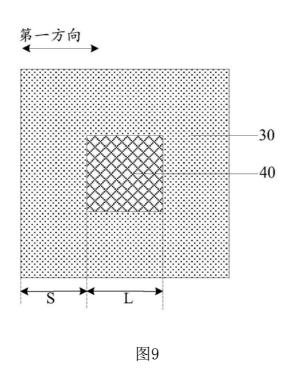

[0027] 图9为图5的俯视示意图;

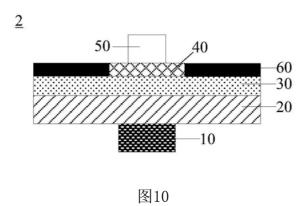

[0028] 图10为本发明实施例提供的一种LED芯片的结构示意图五;

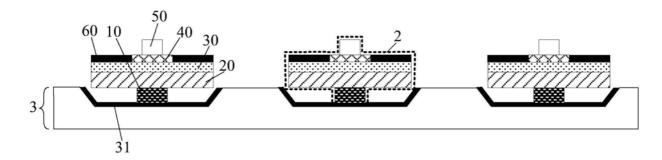

[0029] 图11为本发明实施例提供的一种Micro-LED显示装置的结构示意图;

[0030] 图12为本发明实施例提供的一种LED芯片的制备方法的流程示意图;

[0031] 图13为本发明实施例提供的一种在衬底上形成第一半导体层的结构示意图:

[0032] 图14为本发明实施例提供的一种在衬底上形成多个第一半导体图案的结构示意图:

[0033] 图15为本发明实施例提供的一种在第一半导体图案上形成发光层和第二半导体层的结构示意图:

[0034] 图16为本发明实施例提供的一种在衬底上形成第一半导体图案、发光图案和第二半导体图案的结构示意图:

[0035] 图17为本发明实施例提供的一种在衬底上形成第一半导体层、发光层和第二半导体层的结构示意图;

[0036] 图18为本发明实施例提供的另一种在衬底上形成第一半导体图案、发光图案和第二半导体图案的结构示意图;

[0037] 图19为本发明实施例提供的一种在衬底上形成第一半导体层、发光层以及第二半导体图案的结构示意图:

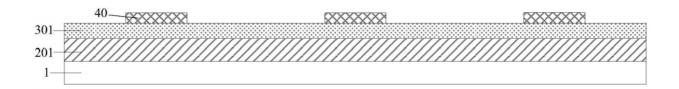

[0038] 图20为本发明实施例提供的一种在衬底上形成第一半导体图案、发光图案和第二辅助半导体图案的结构示意图;

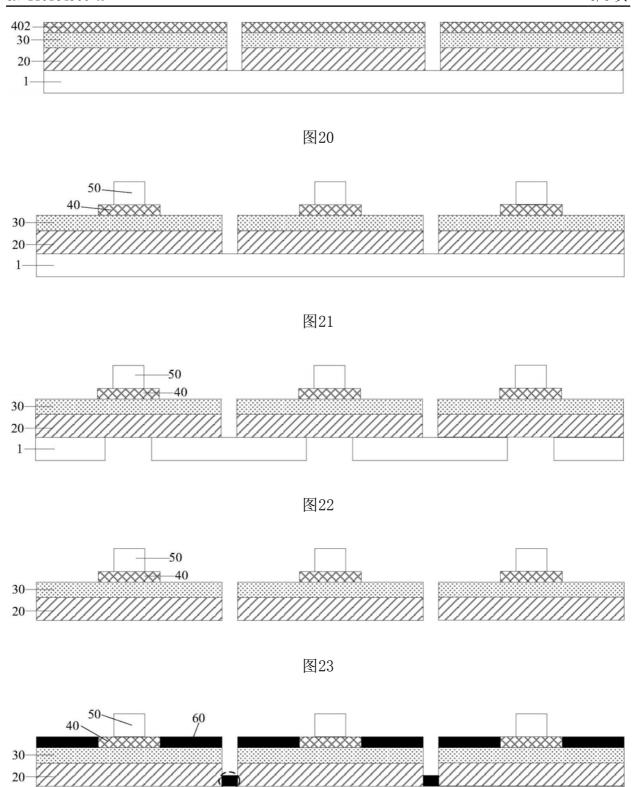

[0039] 图21为本发明实施例提供的一种在第二半导体图案上形成第二电极的结构示意图:

[0040] 图22为本发明实施例提供的一种在衬底上形成过孔的结构示意图:

[0041] 图23为本发明实施例提供的一种去除图21中衬底的结构示意图;

[0042] 图24为本发明实施例提供的一种在第二半导体图案上形成黑矩阵图案的结构示

意图。

[0043] 附图标记:

[0044] 01-像素区域;02-非像素区域;1-衬底;2-LED芯片;3-电路基板;10-第一电极;20-第一半导体图案;201-第一半导体层;30-发光图案;301-发光层;31-驱动电极;40-第二半导体图案;401-第二半导体层;402-第二辅助半导体图案;50-第二电极;60-黑矩阵图案。

#### 具体实施方式

[0045] 下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0046] 本发明实施例提供一种芯片晶圆,如图1所示,包括衬底1以及设置在衬底1上的多个LED芯片2。

[0047] 此处,对于衬底1的材料不进行限定,衬底1的材料例如可以为蓝宝石衬底、硅衬底或氮化镓(GaN)衬底中的一种或多种。

[0048] 本领域技术人员应该明白,对芯片晶圆进行处理可以形成多个相互独立的LED芯片2。对芯片晶圆进行处理,例如可以是如图2所示,去除衬底1,以形成多个独立的LED芯片2。又例如,如图3所示,对衬底1进行切割,以形成多个独立的LED芯片2。多个独立的LED芯片2可以作为光源使用,也可以应用于Micro-LED显示装置。

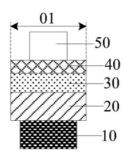

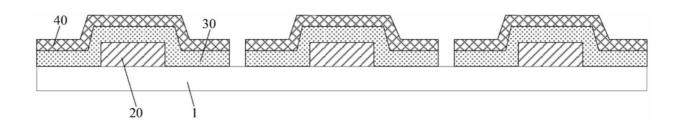

[0049] 基于上述,本发明实施例提供一种LED芯片,如图4、图5以及图6所示,包括依次层叠设置的第一电极10(也可以称为第一欧姆接触电极)、第一半导体图案20、发光图案30、第二半导体图案40以及第二电极50(也可以称为第二欧姆接触电极);第一电极10与第一半导体图案20接触,第二电极50与第二半导体图案40接触;第二电极50为透明电极,第一半导体图案20和/或第二半导体图案40在发光图案30上的正投影的边界位于发光图案30的边界以内;第一半导体图案20、第二半导体图案40以及发光图案30沿LED芯片的厚度方向具有重叠区域。其中,第一半导体图案20为n型半导体,第二半导体图案40为p型半导体;或者,第一半导体图案20为p型半导体,第二半导体图案40为p型半导体;或者,第一半导体图案20为p型半导体,第二半导体图案40为n型半导体。

[0050] 此处,第二电极50为透明电极,第一电极10可以为透明电极,也可以为非透明电极。在第一电极10为透明电极,第二电极50为透明电极的情况下,发光图案30发出的光从第一电极10和第二电极50均可以出射,在此情况下,LED芯片为双面发光型。在第二电极50为透明电极,第一电极10为非透明电极的情况下,发光图案30发出的光从第二电极50出射。

[0051] 第二电极50的材料包括但不限于IZO(Indium Zinc Oxide,氧化铟锌)、ITO (Indium Tin Oxide,氧化铟锡)等。

[0052] 在此基础上,在第二电极50为透明电极,第一电极10为非透明电极的情况下,在一些实施例中,第一电极10为反射电极。在第一电极10为反射电极的情况下,发光图案30发出的光射到第一电极10上后会被第一电极10反射,进而从第二电极50出射,这样一来,可以增强出光,提高了LED芯片的出光效率。

[0053] 在第一电极10为反射电极的情况下,第一电极10的材料包括但不限于Cu(铜)、Au(金)、Ag(银)或Ti(钛)/Al(铝)/Ni(镍)/Au叠层材料等。

[0054] 对于发光图案30的材料不进行限定,发光图案30的材料包括但不限于多量子阱层 (Multiple Quantum Well,简称MQW)。在发光图案30的材料为多量子阱层的情况下,在一些 实施例中,发光图案30的材料为Ⅲ-V族化合物半导体,例如GaN基材料。此外,可以根据发光图案30需要发出光的颜色来选取发光图案30的材料。

[0055] 本发明实施例中,发光图案30的材料为多量子阱层时,可以提高载流子的复合效率,进而提高LED芯片的发光效率。

[0056] 此外,对于第一半导体图案20和第二半导体图案40的材料不进行限定,在一些实施例中,第一半导体图案20和第二半导体图案40的材料为Ⅲ-V族化合物半导体,例如GaN基材料。

[0057] 为了确保第一半导体图案20、发光图案30以及第二半导体图案40在衬底1上生长时的晶格适配以及热适配,因此可选的,第一半导体图案20、第二半导体图案40以及发光图案30的材料均为III-V族化合物半导体。例如第一半导体图案20、第二半导体图案40以及发光图案30的材料均为GaN基材料。

[0058] 此外,对于第一半导体图案20的形状、第二半导体图案40的形状以及发光图案30的形状不进行限定。附图9以第二半导体图案40的形状和发光图案30的形状均为矩形为例进行示意。第二半导体图案40的形状和发光图案30的形状包括但不限于为矩形。例如,第二半导体图案40的形状还可以为圆形,发光图案30的形状还可以为圆形。

[0059] 基于上述,可以是如图4所示,第一半导体图案20在发光图案30上的正投影的边界位于发光图案30的边界以内,第二半导体图案40在发光图案30上的正投影的边界与发光图案30的边界重叠;也可以是如图5所示,第二半导体图案40在发光图案30上的正投影的边界位于发光图案30的边界以内,第一半导体图案20在发光图案30上的正投影的边界与发光图案30的边界重叠;当然还可以是如图6所示,第一半导体图案20和第二半导体图案40在发光图案30上的正投影的边界均位于发光图案30的边界以内。

[0060] 应当理解到,向第一电极10和第二电极50施加电压时,电子和空穴会注入到发光图案30中,在发光图案30中复合发光。由于载流子主要在第一半导体图案20、第二半导体图案40以及发光图案30沿LED芯片厚度方向重叠的区域发生复合,因此发光图案30与第一半导体图案20、第二半导体图案40以及发光图案30沿LED芯片的厚度方向的重叠区域的面积决定着LED芯片的发光面积。发光图案30沿LED芯片的厚度方向的重叠区域的面积决定着LED芯片的发光面积。发光图案30未与第一半导体图案20、第二半导体图案40均正对的区域不发光或发出的光较少。可以将发光图案30与第一半导体图案20、第二半导体图案40均正对的区域,也即,第一半导体图案20、第二半导体图案40以及发光图案30沿LED芯片的厚度方向未完全重叠的区域,也即,发光图案30未与第一半导体图案40以及发光图案30沿LED芯片的厚度方向未完全重叠的区域,也即,发光图案30未与第一半导体图案20、第二半导体图案40均正对的区域称为非像素区域02。参考图4、图5以及图6所示,像素区域01发光,非像素区域02不发光或发出的光较少。

[0061] 参考上述可知,LED芯片2是通过对芯片晶圆进行处理得到的,而芯片晶圆在制备时,先在衬底1上依次生长第一半导体层、发光层、第二半导体层,再对第一半导体层、发光层、第二半导体层进行刻蚀、剥离等形成多个层叠的第一半导体图案20、发光图案30和第二半导体图案40,在刻蚀、剥离等过程中不可避免地会造成LED芯片中的第一半导体图案20、

发光图案30和第二半导体图案40的侧壁结构会受到损伤。

[0062] 由于第一半导体图案20和/或第二半导体图案40在发光图案30上的正投影的边界位于发光图案30的边界以内,而第一半导体图案20、第二半导体图案40以及发光图案30沿LED芯片2的厚度方向重叠的区域为像素区域01,因而对第一半导体层、发光层、第二半导体层进行刻蚀、剥离是在远离像素区域01的位置进行,也即在非像素区域02进行。

[0063] 相关技术提供的LED芯片的结构如图7所示,包括依次层叠设置的第一电极10、第一半导体图案20、发光图案30、第二半导体图案40以及第二电极50,第一半导体图案20、第二半导体图案40在发光图案30上的正投影的边界与发光图案30的边界重叠,即第一半导体图案20、第二半导体图案40以及发光图案30的尺寸相同。由于载流子在第一半导体图案20、第二半导体图案40和发光图案30沿LED芯片厚度方向重叠的区域发生复合,进而发光,而第一半导体图案20、第二半导体图案40在发光图案30上的正投影的边界与发光图案30的边界重叠,因而相关技术中第一半导体图案20、第二半导体图案40以及发光图案30所在的区域均可以发光。

[0064] 由于相关技术中,第一半导体图案20、第二半导体图案40在发光图案30上的正投影的边界与发光图案30的边界重叠,第一半导体图案20、第二半导体图案40以及发光图案30所在的区域均可以发光,因而LED芯片中的第一半导体图案20、发光图案30和第二半导体图案40的侧壁结构受到损伤后,发光图案30的侧壁会形成漏电通道,从而影响LED芯片2的发光效率。

[0065] 本发明实施例提供一种LED芯片2,LED芯片2包括依次层叠设置的第一电极10、第 一半导体图案20、发光图案30、第二半导体图案40以及第二电极50,第一半导体图案20和/ 或第二半导体图案40在发光图案30上的正投影的边界位于发光图案30的边界以内。由于第 一半导体图案20和/或第二半导体图案40在发光图案30上的正投影的边界位于发光图案30 的边界以内,且第一半导体图案20、第二半导体图案40以及发光图案30沿LED芯片的厚度方 向具有重叠区域,因而第一半导体图案20、第二半导体图案40以及发光图案30沿LED芯片的 厚度方向未完全重叠的区域(即非像素区域02)包围第一半导体图案20、第二半导体图案40 以及发光图案30沿LED芯片的厚度方向重叠的区域(即像素区域01),而载流子主要在第一 半导体图案20、第二半导体图案40以及发光图案30沿LED芯片的厚度方向重叠的区域发生 复合并发光(即在像素区域01发生复合并发光),在第一半导体图案20、第二半导体图案40 以及发光图案30沿LED芯片的厚度方向未完全重叠的区域不发生复合或复合的较少(即在 非像素区域不发生复合或复合的较少),因而LED芯片2中的第一半导体图案20、发光图案30 和第二半导体图案40的侧壁结构受到损伤后,对第一半导体图案20、第二半导体图案40以 及发光图案30沿LED芯片的厚度方向重叠的区域的载流子的复合影响较小,因而相对于相 关技术提高了LED芯片2的发光效率。

[0066] 本发明实施例提供的芯片晶圆,如图1所示,包括衬底1以及设置在衬底1上的多个LED芯片2,在LED芯片2为上述的LED芯片的情况下,如图1所示,第一半导体图案20与衬底1接触,第一电极10穿过衬底1上的过孔与第一半导体图案20接触;或者,第二半导体图案40与衬底1接触,第二电极50穿过衬底1上的过孔与第二半导体图案40接触。

[0067] 本发明实施例以在LED芯片的制备过程中,第一半导体图案20相对第二半导体图案40靠近衬底1为例,考虑到如图8所示,第一半导体图案20在发光图案30上的正投影的边

界位于发光图案30的边界以内;或者,第一半导体图案20和第二半导体图案40在发光图案30上的正投影的边界均位于发光图案30的边界以内时,在LED芯片的制备过程中,由于第一半导体图案20的边界位于发光图案30的边界以内,因而在衬底1上生长第一半导体层后,必须对第一半导体层进行构图形成多个第一半导体图案20,之后再在多个第一半导体图案20上生长发光层和第二半导体层,对发光层和第二半导体层进行构图形成多个发光图案30和多个第二半导体图案40。在形成多个第一半导体图案20后,由于相邻第一半导体图案20之间具有凹槽,不平坦,而生长膜层对平坦度的要求较高,因而在第一半导体图案20上生长发光层和第二半导体层时,会影响发光层和第二半导体层的质量,从而影响发光图案30和第二半导体图案40的质量,进而会影响形成的LED芯片2的质量。

[0068] 基于上述,在一些实施例中,如图5所示,第二半导体图案40在发光图案30上的正投影的边界位于发光图案30的边界以内;第一半导体图案20在发光图案30上的正投影的边界与发光图案30的边界重叠。

[0069] 本发明实施例,在LED芯片的制备过程中,在第一半导体图案20靠近衬底1的情况下,由于第二半导体图案40在发光图案30上的正投影的边界位于发光图案30的边界以内;第一半导体图案20在发光图案30上的正投影的边界与发光图案30的边界重叠,因而可以在衬底1上生长完第一半导体层、发光层和第二半导体层之后,再对第一半导体层、发光层和第二半导体层进行构图形成第一半导体图案20、发光图案30以及第二半导体图案40,这样一来,便可以确保形成的第一半导体层、发光层和第二半导体层的质量,进而确保了形成的第一半导体图案20、发光图案30以及第二半导体图案40的质量,从而提高了LED芯片2的质量。

[0070] 在第二半导体图案40在发光图案30上的正投影的边界位于发光图案30的边界以内;第一半导体图案20在发光图案30上的正投影的边界与发光图案30的边界重叠的情况下,考虑到第二半导体图案40在发光图案30上的正投影的边界与靠近该边界的发光图案30的边界沿第一方向的距离S若太小,则第一半导体图案20、发光图案30和第二半导体图案40的侧壁结构受到损伤时,发光图案30的侧壁还是会形成漏电通道,从而影响LED芯片的发光效率。第二半导体图案40在发光图案30上的正投影的边界与靠近该边界的发光图案30的边界沿第一方向的距离S若太大,则LED芯片2的尺寸较大。基于此,在一些实施例中,如图5和图9所示,第二半导体图案40在发光图案30上的正投影的边界与靠近该边界的发光图案30的边界沿第一方向的距离S为第二半导体图案40沿第一方向的长度L的0.5倍~3倍。

[0071] 此处,第一方向可以为任意方向。示例的,如图9所示,第一方向可以为水平方向, 也可以为竖直方向。附图9以第一方向为水平方向为例进行示意。

[0072] 在此基础上,第二半导体图案40在发光图案30上的正投影的边界与靠近该边界的发光图案30的边界沿第一方向的距离S可以为第二半导体图案40沿第一方向的长度L的0.5倍、1倍、1.5倍、2倍或3倍等。

[0073] 参考图5和图9,对于第二半导体图案40在发光图案30上的正投影的边界中左侧的边界,发光图案30左侧的边界靠近第二半导体图案40在发光图案30上的正投影的边界中左侧的边界,计算第二半导体图案40在发光图案30上的正投影的边界与靠近该边界的发光图案30的边界沿第一方向的距离S时,可以计算第二半导体图案40在发光图案30上的正投影的边界中左侧的边界和发光图案30左侧的边界沿第一方向之间的距离。对于第二半导体图

案40在发光图案30上的正投影的边界中右侧的边界,发光图案30右侧的边界靠近第二半导体图案40在发光图案30上的正投影的边界中右侧的边界,计算第二半导体图案40在发光图案30上的正投影的边界与靠近该边界的发光图案30的边界沿第一方向的距离S时,可以计算第二半导体图案40在发光图案30上的正投影的边界中右侧的边界和发光图案30右侧的边界沿第一方向之间的距离。

[0074] 由于第一半导体图案20、第二半导体图案40以及发光图案30沿LED芯片的厚度方向重叠的区域为像素区域01,第一半导体图案20、第二半导体图案40以及发光图案30沿LED芯片的厚度方向未完全重叠的区域为非像素区域02,因而在第二半导体图案40在发光图案30上的正投影的边界位于发光图案30的边界以内;第一半导体图案20在发光图案30上的正投影的边界与发光图案30的边界重叠的情况下,正对第二半导体图案40的区域为像素区域01,除像素区域01以外的区域为非像素区域02。

[0075] 在一些实施例中,如图10所示,LED芯片2还包括设置在第二半导体图案40上的黑矩阵图案(Black Matrix,简称BM)60;第二半导体图案40在黑矩阵图案60上的正投影位于黑矩阵图案60的镂空区域内。

[0076] 此处,黑矩阵图案60也可以称为遮光图案。黑矩阵图案60的材料例如可以为黑色树脂或黑色油墨。

[0077] 本发明实施例,由于LED芯片2包括黑矩阵图案60,第二半导体图案40在黑矩阵图案60上的正投影位于黑矩阵图案60的镂空区域内,因而发光图案30发出的光只能从像素区域01(即正对第二半导体图案40的区域)出射。在LED芯片2应用于Micro-LED显示装置中时,避免了相邻LED芯片2发出的光相互影响。

[0078] 基于上述,本发明实施例提供的LED芯片2可以作为光源使用,还可以应用于Micro-LED显示装置中。本发明实施例提供的LED芯片2可以但不限于作为光源使用或应用于Micro-LED显示装置中。

[0079] 本发明实施例还提供一种Micro-LED显示装置,如图11所示,包括电路基板3以及设置在电路基板3上的多个上述的LED芯片2。

[0080] 如图11所示,电路基板3包括多个凹槽,每个凹槽中设置有驱动电极31,一个LED芯片2设置在一个凹槽中,且LED芯片2的第一电极10或第二电极50与电路基板3上的驱动电极31电连接。

[0081] 在LED芯片2应用于Micro-LED显示装置中时,可以根据Micro-LED显示装置中亚像素区域的大小来相应设计LED芯片2中第一半导体图案20、第二半导体图案40以及发光图案30沿LED芯片2的厚度方向的重叠区域的面积。

[0082] 本发明实施例提供的Micro-LED显示装置是一种新型的自发光型显示技术,与LCD (Liquid Crystal Display,液晶显示装置)相比,Micro-LED显示装置结构更为简单,且 Micro-LED显示装置作为自发光技术,在显示对比度、响应速度、色域、视角等方面优于LCD。与OLED (Organic Light-Emitting Diode,有机电致发光二极管)显示装置相比,Micro-LED显示装置在亮度、发光效率以及寿命等方面具有一定优势。

[0083] 本发明实施例还提供一种LED芯片2的制备方法,如图12所示,包括:

[0084] S100、在衬底1上形成多个层叠设置的第一半导体图案20、发光图案30和第二半导体图案40;第一半导体图案20和/或第二半导体图案40在发光图案30上的正投影的边界位

于发光图案30的边界以内。第一半导体图案20为n型半导体,第二半导体图案40为p型半导体;或者,第一半导体图案20为p型半导体,第二半导体图案40为n型半导体。

[0085] 此处,可以是第一半导体图案20在发光图案30上的正投影的边界位于发光图案30的边界以内。也可以是第二半导体图案40在发光图案30上的正投影的边界位于发光图案30的边界以内。当然还可以是第一半导体图案20和第二半导体图案40在发光图案30上的正投影的边界均位于发光图案30的边界以内。

[0086] 在第一半导体图案20在发光图案30上的正投影的边界位于发光图案30的边界以内,第二半导体图案40在发光图案30上的正投影的边界与发光图案30的边界重叠的情况下,在衬底1上形成多个层叠设置的第一半导体图案20、发光图案30和第二半导体图案40,包括:

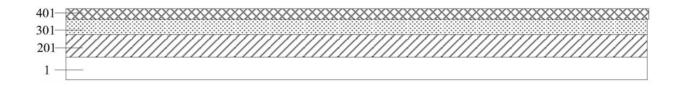

[0087] S200、如图13所示,在衬底1上形成(例如生长)第一半导体层201。

[0088] S201、如图14所示,对第一半导体层201进行构图,以形成多个第一半导体图案20。

[0089] 本发明实施例提到的"构图"均可以包括刻蚀、剥离等过程。

[0090] 在此基础上,可以根据LED芯片2的发光面积(即像素区域的面积)来确定第一半导体图案20的面积。

[0091] S202、如图15所示,在第一半导体图案20上依次形成(例如生长)发光层301、第二半导体层401。

[0092] S203、如图16所示,对发光层301、第二半导体层401同时进行构图,以形成多个发光图案30和多个第二半导体图案40;第一半导体图案20、发光图案30、第二半导体图案40依次层叠设置,且第一半导体图案20在发光图案30上的正投影的边界位于发光图案30的边界以内。

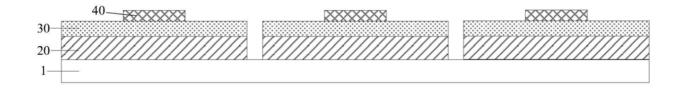

[0093] 在第二半导体图案40在发光图案30上的正投影的边界位于发光图案30的边界以内,第一半导体图案20在发光图案30上的正投影的边界与发光图案30的边界重叠的情况下,在衬底1上形成多个层叠设置的第一半导体图案20、发光图案30和第二半导体图案40,包括:

[0094] S300、如图17所示,在衬底1上依次形成(例如生长)第一半导体层201、发光层301和第二半导体层401。

[0095] S301、如图18所示,对第一半导体层201、发光层301和第二半导体层401进行构图 形成多个层叠设置的第一半导体图案20、发光图案30和第二半导体图案40。第二半导体图案40在发光图案30上的正投影的边界位于发光图案30的边界以内,第一半导体图案20在发光图案30上的正投影的边界与发光图案30的边界重叠。

[0096] 上述的S301可以通过以下两种方式实现。

[0097] 第一种:S301包括:

[0098] S400、如图19所示,对第二半导体层401进行构图,以形成多个第二半导体图案40。

[0099] S401、如图18所示,对第一半导体层201和发光层301同时进行构图,以形成多个发光图案30和多个第一半导体图案20;第二半导体图案40在衬底1上的正投影的边界位于发光图案30在衬底1上的正投影的边界以内。

[0100] 第二种:S301包括:

[0101] S500、如图20所示,对第一半导体层201、发光层301、第二半导体层401同时进行构

图,以形成多个第一半导体图案20、多个发光图案30以及多个第二辅助半导体图案402。

[0102] S501、如图18所示,对多个第二辅助半导体图案402进行构图,以形成多个第二半导体图案40。

[0103] 对比形成第一半导体图案20、发光图案30和第二半导体图案40的方法S400~S401和方法S500~S501可知,S400和S501只需要对一层进行构图,S401需要对两层同时进行构图,而S500需要对三层同时构图,由于对三层同时进行构图,因厚度增加会增加构图时间,因而相对于方法S500~S501,方法S400~S401提高了形成第一半导体图案20、发光图案30和第二半导体图案40的效率。

[0104] 在第一半导体图案20和第二半导体图案40在发光图案30上的正投影的边界均位于发光图案30的边界以内的情况下,在衬底1上形成多个层叠设置的第一半导体图案20、发光图案30和第二半导体图案40,包括上述的S200~S202,还包括下述的S204~S205或者S206~S207。

[0105] S204、对第二半导体层401进行构图,以形成多个第二半导体图案40。

[0106] S205、对发光层301进行构图形成多个发光图案30。

[0107] S206、对第二半导体层401和发光层301同时进行构图,形成多个发光图案30和多个第二辅助半导体图案402。

[0108] S207、对第二辅助半导体图案402进行构图,以形成多个第二半导体图案40。

[0109] S101、如图21所示,在每个第二半导体图案40上形成第二电极50;第二电极50与第二半导体图案40接触;第二电极50为透明电极。

[0110] 对于形成第二电极50的方法不进行限定,例如,可以利用具有图案的蒸镀掩膜板在每个第二半导体图案40上通过蒸镀形成第二电极50。又例如,可以通过形成导电薄膜、掩膜曝光、显影以及刻蚀的工艺在每个第二半导体图案40远离发光图案30的一侧形成第二电极50。

[0111] 此外,上述实施例已经对第二电极50的材料进行了详细的描述,此处不再赘述。

[0112] S102、在每个第一半导体图案20远离发光图案30的一侧形成第一电极10,第一电极10与第一半导体图案20接触,并去除衬底1,以形成多个LED芯片2。

[0113] 此处,对于形成第一电极10的方法不进行限定,例如,可以利用具有图案的蒸镀掩膜板在每个第一半导体图案20远离发光图案30的一侧通过蒸镀形成第一电极10。又例如,可以通过形成导电薄膜、掩膜曝光、显影以及刻蚀的工艺在每个第一半导体图案20远离发光图案30的一侧形成第一电极10。

[0114] 在此基础上,上述实施例已经对第一电极10的材料进行了详细的描述,此处不再 赘述。

[0115] 上述的S102可以通过以下两种方式实现。

[0116] 第一种:

[0117] S600、如图22所示,在衬底1上形成多个过孔,以露出每个第一半导体图案20。

[0118] 此处,可以对衬底1进行刻蚀,并刻蚀到第一半导体图案20,以形成过孔。

[0119] S601、如图1所示,在每个过孔处形成第一电极10,第一电极10穿过衬底1上的过孔与第一半导体图案20接触。

[0120] 通过S100~S601可以制备得到芯片晶圆,即S100、S101、S600以及S601为芯片晶圆

的制备方法。

[0121] S602、如图2所示,去除衬底1,以形成多个LED芯片2。

[0122] 此处,可以通过激光照射衬底1等方法去除衬底1,即将衬底1与第一半导体图案20分离开。

[0123] 第二种:

[0124] S700、如图23所示,去除衬底1。

[0125] 此处,去除衬底1的方法可以参考上述,此处不再赘述。

[0126] S701、在第二电极50远离第二半导体图案40的一侧设置固定基板,每个第二电极50与固定基板固定连接。

[0127] S702、如图2所示,形成多个第一电极10,一个第一半导体图案20与至少一个第一电极10接触。

[0128] S703、去除固定基板,以形成多个LED芯片2。

[0129] 本发明实施例提供一种LED芯片2的制备方法,LED芯片2的制备方法与上述的LED芯片2具有相同的结构和有益效果,由于上述实施例已经对LED芯片2的结构和有益效果进行了详细的描述,因而此处不再赘述。

[0130] 在形成第二半导体图案40之后,去除衬底1之前,LED芯片的制备方法还包括:

[0131] S103、如图24所示,在第二半导体图案40上形成黑矩阵图案60,第二半导体图案40 在衬底1上的正投影位于黑矩阵图案60的镂空区域在衬底1上的正投影内。

[0132] 此处,S103可以在S100之后,S101之前。S103也可以在S101之后,S102之前。当然,S103还可以在S102之后。在S103在S102之后的情况下,应采用S600~S602在每个第一半导体图案20远离发光图案30的一侧形成第一电极10,并去除衬底1,且S103在S602之前。

[0133] 在此基础上,可以利用具有图案的掩膜板对第二半导体图案40所在的区域进行遮挡,在第二半导体图案40以外的区域形成遮光材料,以形成遮光黑矩阵图案60。也可以在第二半导体图案40上形成一层遮光层,对遮光层进行掩膜曝光,以形成黑矩阵图案60。

[0134] 为了确保去除衬底1后可以形成多个独立的LED芯片2,因而在一些实施例中,在形成黑矩阵图案60时,黑矩阵图案60正对相邻第一半导体图案20之间的部分镂空。在另一些实施例中,如图24所示,在形成黑矩阵图案60之后,对黑矩阵图案60中位于相邻第一半导体图案20之间部分(如图24中虚线圈所示)进行刻蚀。

[0135] 以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

图1

图2

图3

图4

冬

图6

图7

图11

在衬底上形成多个层叠设置的第一半导体图案、发光图案和第二半导体图案;所述第一半导体图案和/或所述第二半导体图案在所述发光图案上的正投影的边界位于所述发光图案的边界以内;所述第一半导体图案为n型半导体,所述第二半导体图案为p型半导体,所述第二半导体图案为n型半导体

-S100

在每个所述第二半导体图案上形成第二电极; 所述第二电极与所述第二半导体图案接触; 所述第二电极为透明电极;

-S101

在每个所述第一半导体图案远离所述发光图案的一侧形成第一电极,所述第一电极与所述第一半导体图案接触,并去除 所述衬底,以形成多个LED芯片 -S102

## 图12

图13

图14

图15

图16

图17

图18

图19

图24

| 专利名称(译) I      | LED芯片及其制备方法、芯片晶圆、Micro-LED显示装置   |         |            |  |

|----------------|----------------------------------|---------|------------|--|

| 公开(公告)号        | CN110164900A                     | 公开(公告)日 | 2019-08-23 |  |

| 申请号            | CN201910456585.0                 | 申请日     | 2019-05-29 |  |

| [标]申请(专利权)人(译) | 京东方科技集团股份有限公司                    |         |            |  |

| 申请(专利权)人(译)    | 京东方科技集团股份有限公司                    |         |            |  |

| 当前申请(专利权)人(译)  | 京东方科技集团股份有限公司                    |         |            |  |

| :              | 侯孟军<br>李延钊<br>孟虎<br>刘宗民          |         |            |  |

| :              | 侯孟军<br>李延钊<br>孟虎<br>刘宗民          |         |            |  |

| IPC分类号 I       | H01L27/15 H01L33/00 H01L33/20    |         |            |  |

| CPC分类号         | H01L27/156 H01L33/0095 H01L33/20 |         |            |  |

| 代理人(译)         | 申健                               |         |            |  |

|                | Espacenet SIPO                   |         |            |  |

#### 摘要(译)

本发明实施例提供一种LED芯片及其制备方法、芯片晶圆、Micro-LED显 = 示装置,涉及显示技术领域,可以探讨。 示装置,涉及显示技术领域,可以解决LED芯片侧壁受损形成漏电通 道,进而影响LED芯片的发光效率的问题。该LED芯片包括依次层叠设 置的第一电极、第一半导体图案、发光图案、第二半导体图案以及第二 电极;第一电极与第一半导体图案接触,第二电极与第二半导体图案接 触,第二电极为透明电极;第一半导体图案和/或第二半导体图案在发光 图案上的正投影的边界位于发光图案的边界以内;第一半导体图案、第 二半导体图案以及发光图案沿LED芯片的厚度方向具有重叠区域;第一 半导体图案为n型半导体,第二半导体图案为p型半导体;或者,第一半 导体图案为p型半导体,第二半导体图案为n型半导体。